岐阜大学工学部応用情報学科 加藤研究室

画像処理・パターン認識

並列演算器による画像処理の高速化

画像処理の分野では、高速なプロセッサへの要求が高まっています。近年、その高速なプロセッサのアーキテクチャとして並列演算器が注目を集めています。しかし、単純に今までの逐次プログラムを並列演算器上で動かすだけでは高速化されないため、その演算器に最適な並列プログラムへ改良する必要があります。そこで本研究では、SIMD、画像処理専用プロセッサ、マルチコアプロセッサの代表的な3つの並列演算アーキテクチャの特性を考察しました。1.並列演算アーキテクチャの分類

本研究では、3つの並列演算アーキテクチャの代表例として以下の並列演算器を用いました。

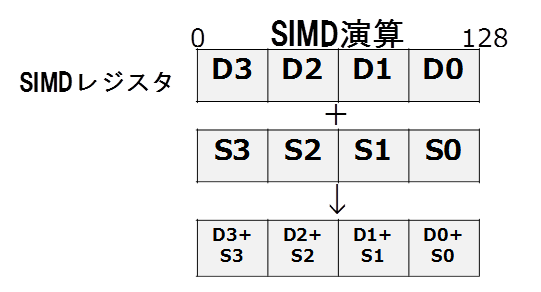

○SSE命令セット

一度に複数のデータを格納できる128ビット幅レジスタを用いてSIMD演算を実現します。

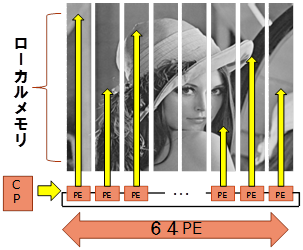

○IMAPCAR

64個の演算機構からなる画像処理専用プロセッサです。演算機構ひとつひとつがローカルなメモリを保持しており、制御機構からの命令をそれぞれで実行することで並列演算を行います。

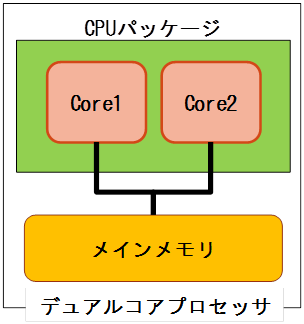

○汎用マルチコアプロセッサ

複数の汎用プロセッサを1つのパッケージに集積し、メモリを全コアで共有する共有メモリ型マルチプロセッサです。最近の汎用コンピュータでも実装されています。

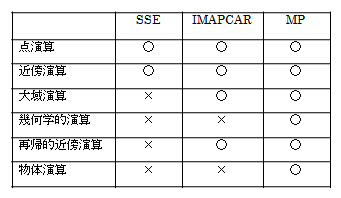

2.画像処理の実装可能性

画像認識処理アルゴリズムの内、低~中レベルの処理について画素参照パターンに元に点演算、近傍演算、大域演算、幾何学的演算、再帰的近傍演算、物体演算の6つに分類されます。これらの分類の3つの並列演算器での実装可能性について考察しました。

SSE:

最大で連続した128ビット分の画素への処理を一度に実行できます。

IMAPCAR:

各PEは各自のローカルメモリへしかアクセスできないが、それぞれで異なったアドレスへアクセスすることができます。

汎用マルチコアプロセッサ:

全コアでメモリを共有できるため各コアは独立して動作できるためランダムなアクセスが可能です。

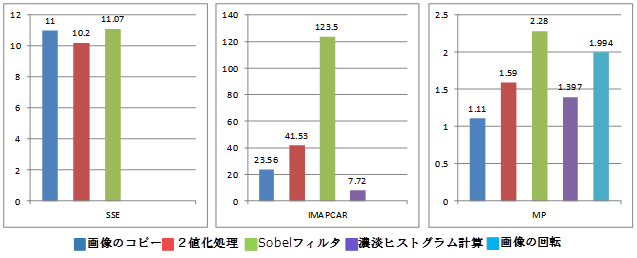

3.高速化率に対する考察

実際に並列演算器で逐次と並列プログラムを組みどれだけ高速化できるのかを計測しました。

SSEは、実装可能なプログラムが少ないものの高速化率はどの処理も高い値となっています。また、IMAPCARは、フィルタ処理の高速化率が高いのは隣接した演算機構同士でデータの受け渡しができるためであると考えられます。マルチコアプロセッサは、画像のコピー、2値化処理での高速化率が低い値となっています。これは、メインメモリへのアクセスは、1つのコアからしかできないためメモリアクセスの割合が大きな処理には不向きであると考えられます。

4.今後の課題

何らかの新しいシステムをIMAPCARなどの並列演算器に実装し、高速化、小型化、消費電力化を目指します。